Broadcom та Apple створюють процесори для задач AI

2025-01-17

De Novo Cloud Expert

Компанію Broadcom, відома своїм потужним науково-технічним потенціалом, обрано як партнера Apple зі створення нового серверного процесора під кодовою назвою Baltra. Вихід готових чіпів очікується у 2026 році.

Нещодавно ми писали про те, що Broadcom допоможе компанії OpenAI у розробці нового процесора, орієнтованого на завдання штучного інтелекту, а вже в середині грудня стало відомо, що цей приклад не поодинокий. Broadcom стала ще й технічним партнером компанії Apple, яка, як і OpenAI, хоче розробити власний серверний чіп, орієнтований на навантаження AI/ML. Вибір партнерів є цілком логічним — як Broadcom, так й Apple мають великий досвід розробки в цій сфері. Щобільше, компанії спільно працюють над створенням електронних компонентів для 5G. Своєю чергою, Broadcom має потужну науково-технічну базу та регулярно представляє нові технології в галузі процесорів.

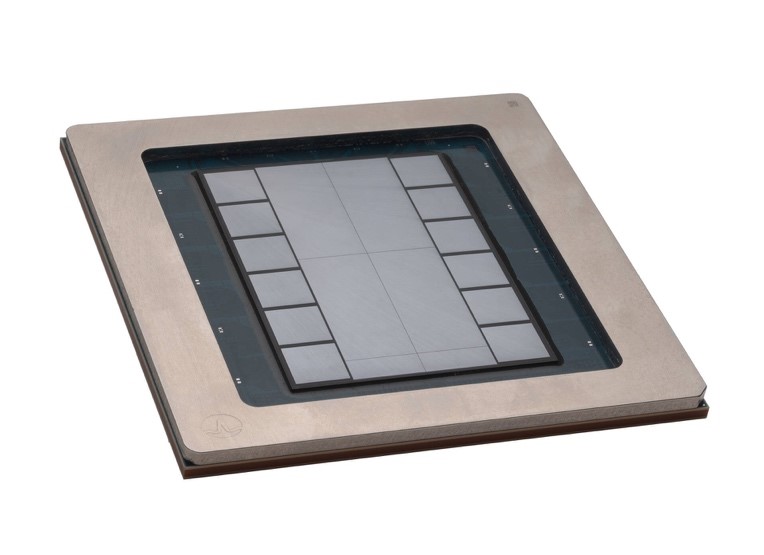

Наприклад, на конференції, яка пройшла нещодавно, Hot Chips було продемонстровано чіплети оптичного інтерконекту, що дозволяють об'єднати прискорювачі обчислень (GPU/TPU) для підтримки великих кластерів, що масштабуються, та забезпечення обміну даними на терабітних швидкостях. Крім того, компанія продемонструвала власну нову технологію 3.5D-пакування (packaging), яка може допомогти виробникам мікросхем вийти за межі нинішніх технологічних обмежень, пов'язаних з компонуванням елементів процесора. Фірмова технологія Broadcom 3.5D eXtreme Dimension System in Package (3.5D XDSiP) відкрита для ліцензування і на її основі інші компанії можуть створювати власні потужніші та компактні чіпи.

Тому, швидше за все, Apple планує використати технологію 3.5D XDSiP для створення перспективного процесора Baltra. Відомих деталей про майбутній чіп, поки небагато, проте на основі наявних відомостей, можна припустити, що він буде заснований на архітектурі ARM і буде оснащений великою кількістю спеціалізованих ядер, оптимізованих для виконання операцій, характерних для завдань штучного інтелекту (матричне обчислення, нейронні мережі згортки тощо).

Також, ймовірно, що для прискорення обчислень з рухомою комою, які широко використовуються в алгоритмах машинного навчання, процесор буде оснащений векторними та тензорними ядрами, а для забезпечення високої пропускної спроможності даних та зниження затримок процесор, ймовірно, буде інтегрований з високошвидкісною пам'яттю HBM (High Bandwidth Memory). Водночас експерти оцінюють повний час розробки такого рішення у 1,5-2 роки, таким чином нові ШІ-процесори навряд чи потраплять до серійного виробництва раніше 2026 року.